Tom Kelliher, CS 240

Apr. 25, 2012

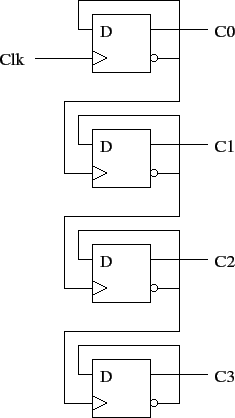

Shift registers.

Memory.

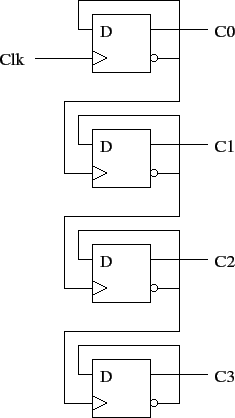

The increment ripples -- propagation delay problems.

Slow counters.

Basic idea:

32 bit up counter with enable and reset.

-- Up counter with enable and reset

--

-- Note how en must be handled after the flip-flop generating

-- code.

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity counter is

port (

clk, reset_n, en : in std_logic;

q : out std_logic_vector (31 downto 0);

co : out std_logic);

end counter;

architecture behavioral of counter is

signal count : std_logic_vector (31 downto 0);

begin -- behavioral

q <= count;

state: process (clk, reset_n)

begin -- process state

if reset_n = '0' then

count <= X"00000000";

elsif clk'event and clk = '1' then

if en = '1' then

count <= count + X"00000001";

end if;

end if;

end process state;

carry_out: process (count, en)

begin -- process carry_out

if count = X"FFFFFFFF" and en = '1' then

co <= '1';

else

co <= '0';

end if;

end process carry_out;

end behavioral;