Inside RAM

Tom Kelliher, CS 240

May 7, 2008

Final: Tuesday, May 13, 3:00-5:00 pm.

None.

Introduction to memory; ROM; FLASH.

- Introduction.

- Static RAM.

- Dynamic RAM.

Final.

- Organizations of RAMs: number of words, bits/word.

- Operation:

- Not enabled: low power mode, output in high-impedance state

(disconnected)

- Read: A single word should be read. Address may change.

- Write: A single word should be written. Address must be stable.

- Refresh. Hidden or not hidden?

- RAM will have a 2-D structure: row/word, column/bit.

The number of columns may not have anything to do with bits/word -- many

RAMs have 1 bit/word but are 2-D internally.

- RAMS consist of:

- Storage cells.

- Word and bit decoders.

- Write logic.

- Read logic (sense amp).

- Refresh logic for DRAMs.

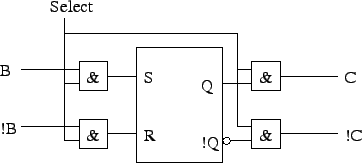

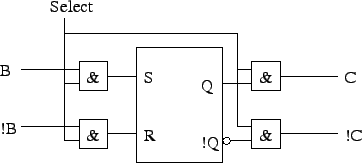

- Memory cell model:

Goal: cell should be as small as possible, to increase storage density.

Think about the AND gates on the output side as tri-state buffers --

transmission gates.

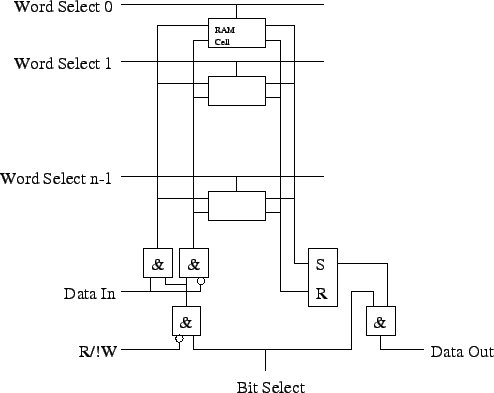

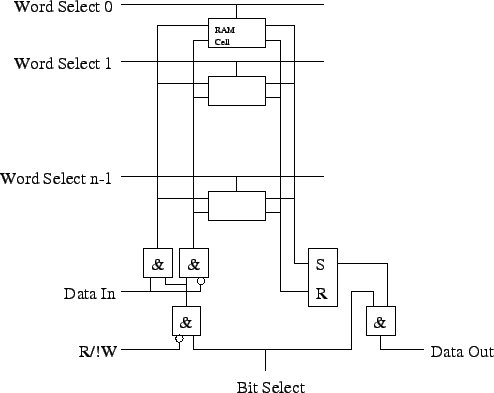

- Bit slice of a RAM array:

- Assume you have

bit-slice RAM cells. Adding 2-to-4

decoders, how would a

bit-slice RAM cells. Adding 2-to-4

decoders, how would a  RAM look? A

RAM look? A  RAM?

RAM?

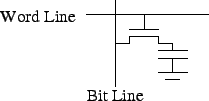

- DRAM cell:

- SRAM cell: five or six transistors. DRAM cell: one transistor and

one capacitor.

- Bit-Slice: support structure similar.

- Bit line has higher capacitance than storage capacitor -- sense amps.

- Destructive read. Use of sense amps to restore data.

- Refresh due to leakage. Refresh logic.

Thomas P. Kelliher

2008-05-05

Tom Kelliher