There will always be some asynchronous elements in a circuit which interfaces to the real world environment.

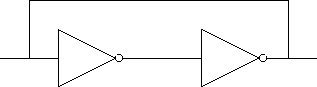

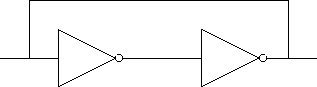

Non-overlapping clocks.

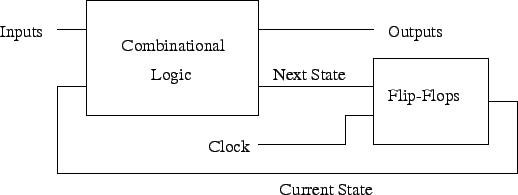

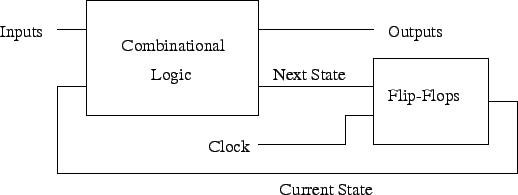

This is the basic idea, to be modified for actual use.

Tom Kelliher, CS 240

Mar. 28, 2008

Read 5-3.

Finished Xilinx introduction lab.

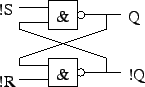

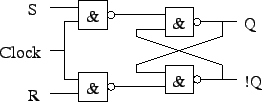

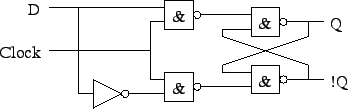

Flip-flops

There will always be some asynchronous elements in a circuit which interfaces to the real world environment.

Non-overlapping clocks.

This is the basic idea, to be modified for actual use.

Behavior.

Latched when clock is low.

A solution: non-overlapping clocks. (Achieved with master-slave flip-flops.)

(Think of this as a logic primitive.)