# Computer Architecture

Building a Modern Computer From First Principles

www.nand2tetris.org

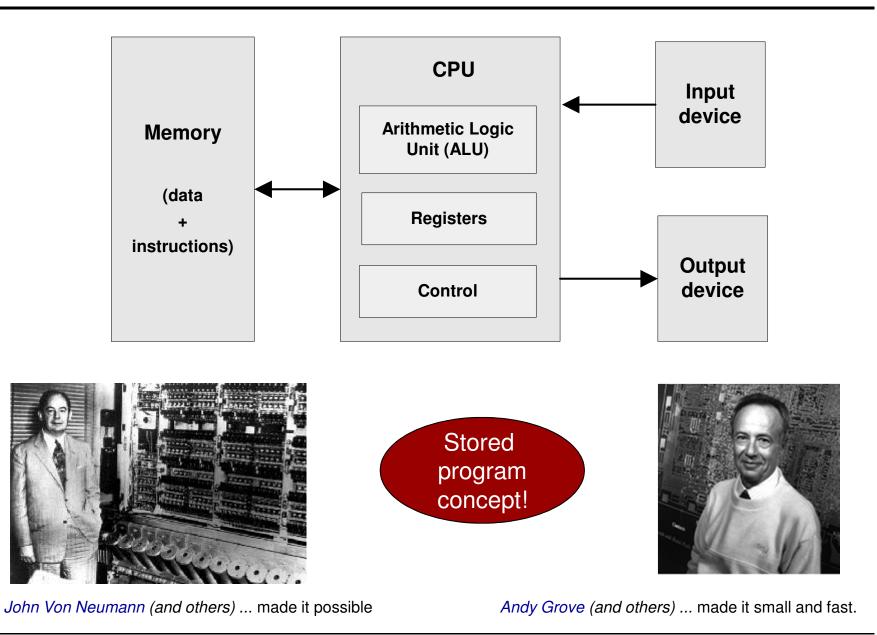

## Von Neumann machine (circa 1940)

## Processing logic: the instruction cycle

Executing the *current instruction* involves one or more of the following micro-tasks:

- □ Fetch the next instruction

- Decode the instruction

- □ Read source operands

- Perform ALU operation

- Store the result

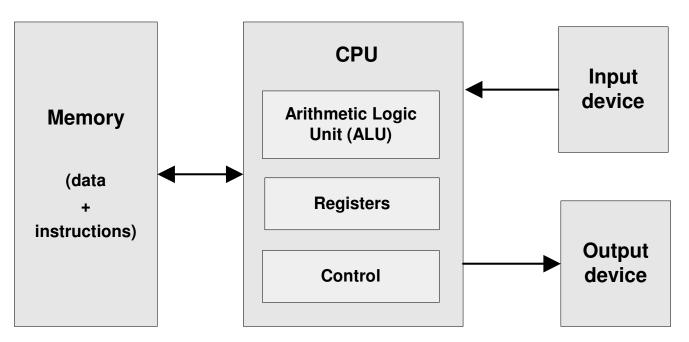

## The Hack computer

- A 16-bit Von Neumann platform

- The instruction memory and the data memory are physically separate

- Screen: 512 columns by 256 rows, black and white

- Keyboard: standard

- Designed to execute programs written in the Hack machine language

- Can be easily built from the chip-set that we built so far in the course

#### Main parts of the Hack computer:

- Instruction memory (ROM)

- □ Memory (RAM):

- Data memory

- Screen (memory map)

- Keyboard (memory map)

- □ CPU

- Computer (the logic that holds everything together).

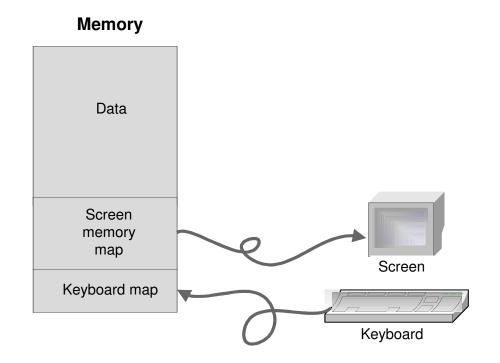

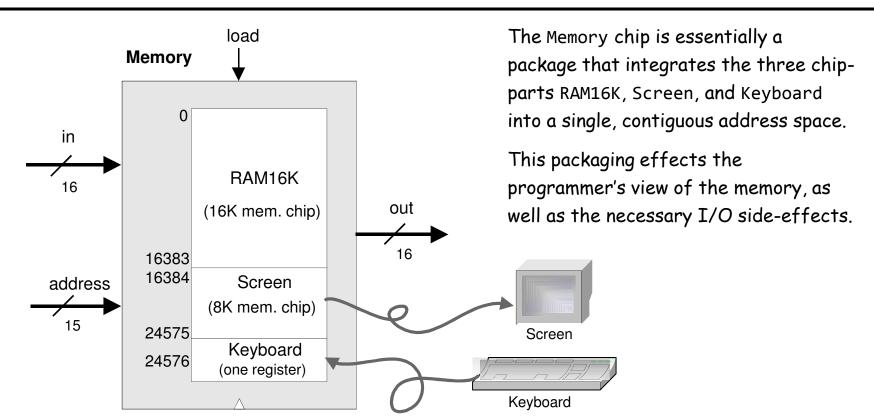

#### Using the memory:

- To record or recall values (e.g. variables, objects, arrays), use the first 16K words of the memory

- □ To write to the screen (or read the screen), use the next 8K words of the memory

- □ To read which key is currently pressed, use the next word of the memory.

### Memory: physical implementation

#### Access logic:

- □ Access to any address from 0 to 16,383 results in accessing the RAM16K chip-part

- Access to any address from 16,384 to 24,575 results in accessing the Screen chip-part

- Access to address 24,576 results in accessing the keyboard chip-part

- Access to any other address is invalid.

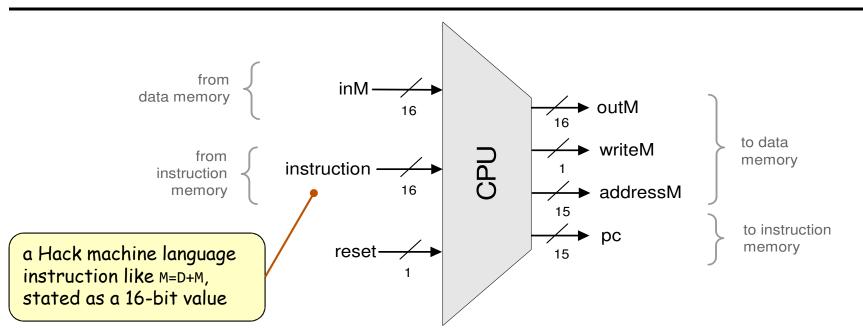

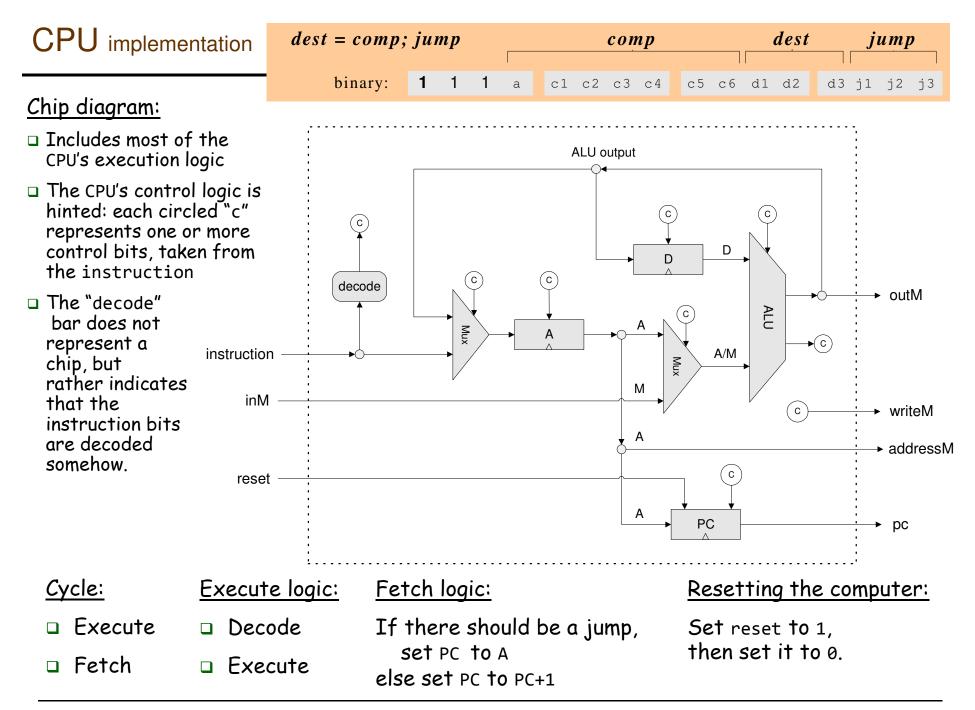

CPU

<u>CPU internal components (invisible in this chip diagram)</u>: ALU and 3 registers: A, D, PC

#### CPU fetch logic:

Recall that:

1. the instruction may include a jump directive (expressed as non-zero jump bits)

2. the ALU emits two control bits, indicating if the ALU output is zero or less than zero

<u>If reset==0:</u> the CPU uses this information (the jump bits and the ALU control bits) as follows: If there should be a jump, the PC is set to the value of A; else, PC is set to PC+1 <u>If reset==1:</u> the PC is set to 0. (restarting the computer)

| dest = comp; | comp |   |   |   |    |    |    |    | dest |    |    | jump |     |    |    |    |

|--------------|------|---|---|---|----|----|----|----|------|----|----|------|-----|----|----|----|

|              |      |   |   |   |    |    |    |    |      |    |    |      |     |    |    |    |

| binary:      | 1    | 1 | 1 | a | c1 | с2 | с3 | с4 | с5   | с6 | d1 | d2   | d 3 | j1 | j2 | ј3 |

| (when a=0) | hen a=0) |    |    | (when a=1) | d1 | d2 | d3   | Mnemonic        | Destination                       | Destination (where to store the computed value) |           |                                            |                 |                        |  |  |

|------------|----------|----|----|------------|----|----|------|-----------------|-----------------------------------|-------------------------------------------------|-----------|--------------------------------------------|-----------------|------------------------|--|--|

| comp       | c1       | c2 | c3 | c4         | с5 | С6 | comp | 0               | 0                                 | 0                                               | null      | The value is                               | s not stored an | ywhere                 |  |  |

| 0          | 1        | 0  | 1  | 0          | 1  | 0  |      | Ο               | Ο                                 | 1                                               | м         | Memory[A] (memory register addressed by A) |                 |                        |  |  |

| 1          | 1        | 1  | 1  | 1          | 1  | 1  |      | Ο               | 1                                 | ο                                               | D         | D register                                 |                 |                        |  |  |

| -1         | 1        | 1  | 1  | 0          | 1  | 0  |      | ο               | 1                                 | 1                                               | MD        | Memory[A] and D register                   |                 |                        |  |  |

| D          | 0        | 0  | 1  | 1          | 0  | Ο  |      | _               |                                   |                                                 |           |                                            |                 |                        |  |  |

| A          | 1        | 1  | 0  | 0          | 0  | Ο  | м    | 1 0 0 Å         |                                   |                                                 | A         | A register                                 |                 |                        |  |  |

| ! D        | o        | ο  | 1  | 1          | 0  | 1  |      | 1               | 1 0 1 AM A register and Memory[A] |                                                 |           |                                            |                 |                        |  |  |

| ٨!         | 1        | 1  | 0  | 0          | 0  | 1  | ! M  | 1               | 1                                 | 0                                               | AD        | A register and D register                  |                 |                        |  |  |

| - D        | 0        | 0  | 1  | 1          | 1  | 1  |      | 1               | 1                                 | 1                                               | AMD       | A register, Memory[A], and D register      |                 |                        |  |  |

| -A         | 1        | 1  | 0  | 0          | 1  | 1  | - M  |                 |                                   |                                                 | I         | 1 –                                        |                 |                        |  |  |

| D+1        | o        | 1  | 1  | 1          | 1  | 1  |      |                 | j1 j2                             |                                                 | j3        | Mnemonic                                   | Effect          |                        |  |  |

| A+1        | 1        | 1  | ο  | 1          | 1  | 1  | M+1  | ( <i>out</i> <0 |                                   | 0)                                              | (out = 0) | (out > 0)                                  | TATIENTOULIC    |                        |  |  |

| D-1        | o        | ο  | 1  | 1          | 1  | ο  |      | 0               |                                   |                                                 | Ο         | Ο                                          | null            | No jump                |  |  |

| A-1        | 1        | 1  | о  | ο          | 1  | о  | M-1  | 0               |                                   |                                                 | Ο         | 1                                          | JGT             | If <i>out</i> > 0 jump |  |  |

| D+A        | o        | ο  | о  | ο          | 1  | ο  | D+M  | 0               |                                   |                                                 | 1         | Ο                                          | JEQ             | If <i>out</i> = 0 jump |  |  |

| D-A        | o        | 1  | ο  | ο          | 1  | 1  | D-M  |                 | 0                                 |                                                 | 1         | 1                                          | JGE             | If <i>out</i> ≥0 jump  |  |  |

| A-D        | o        | ο  | ο  | 1          | 1  | 1  | M-D  |                 | 1                                 |                                                 | Ο         | Ο                                          | JLT             | If <i>out</i> <0 jump  |  |  |

| DEA        | 0        | 0  | 0  | 0          | 0  | 0  | Dem  |                 | 1                                 |                                                 | Ο         | 1                                          | JNE             | If <i>out</i> ≠ 0 jump |  |  |

| DIA        | o        | 1  | o  | 1          | ō  | 1  | DIM  |                 | 1                                 |                                                 | 1         | Ο                                          | JLE             | If <i>out</i> ≤0 jump  |  |  |

| 21         |          | -  | -  | -          | -  | -  | - ,  |                 | 1                                 |                                                 | 1         | 1                                          | JMP             | Jump                   |  |  |

Elements of Computing Systems, Nisan & Schocken, MIT Press, <u>www.nand2tetris.org</u>, Chapter 5: Computer Architecture

Elements of Computing Systems, Nisan & Schocken, MIT Press, www.nand2tetris.org, Chapter 5: Computer Architecture

- Pipelining

- Caching

- More I/O units

- Special-purpose processors (I/O, graphics, communications, ...)

- Multi-core / parallelism; GPUs

- Efficiency

- Energy consumption considerations

- And more ...

Perspective: some issues we haven't discussed (among many)

- CISC / RISC (hardware / software trade-off)

- Hardware diversity: desktop, laptop, mobile, game machines, ...

- General-purpose vs. embedded computers